アジャイル開発

AI時代のチップ開発法

2020.05.11

ウォーターフォール型からアジャイル型へ

アジャイル(Agile)とは、「素早い」「機敏」という意味です。

システムやソフトウェアの開発は、 従来ウォーターフォールモデルが主流でした。最初に仕様と計画を決定し、計画に従ってトップダウンに開発・実装していく手法です。前の工程には戻らない前提なので、下流から上流へは戻らない水の流れにたとえてウォーターフォールと呼びます。

これと逆のアプローチ、つまり小さな単位で実装とテストを繰り返して開発を進めるボトムアップの手法がアジャイル開発です。2001年に新たな手法として登場しました。ウォーターフォールに比べて開発期間を短縮できることが多く、アジャイルと呼ばれています。

開発途中でも仕様の変更や追加が可能な点もアジャイル開発のメリットです。一方で、開発の方向性がブレやすい、全体像を把握しにくくスケジュール管理が難しい、というデメリットもあります。

開発途中に仕様や設計の変更は当然あり得るという前提に立てば、計画段階で厳密な仕様を決めるのではなく大体の仕様だけを決めておき、途中で変更があった場合に臨機応変に対処できる柔軟性(resilience)を備えた方が顧客のニーズに応えることができます。

大体の仕様と計画を決めたら、システムを小さな単位に分けて、「計画」「設計」「実装」「テスト」を行いながら、1〜4週間程度の期間内で機能のリリースを繰り返します。

一方、チップの設計はトップダウンです。

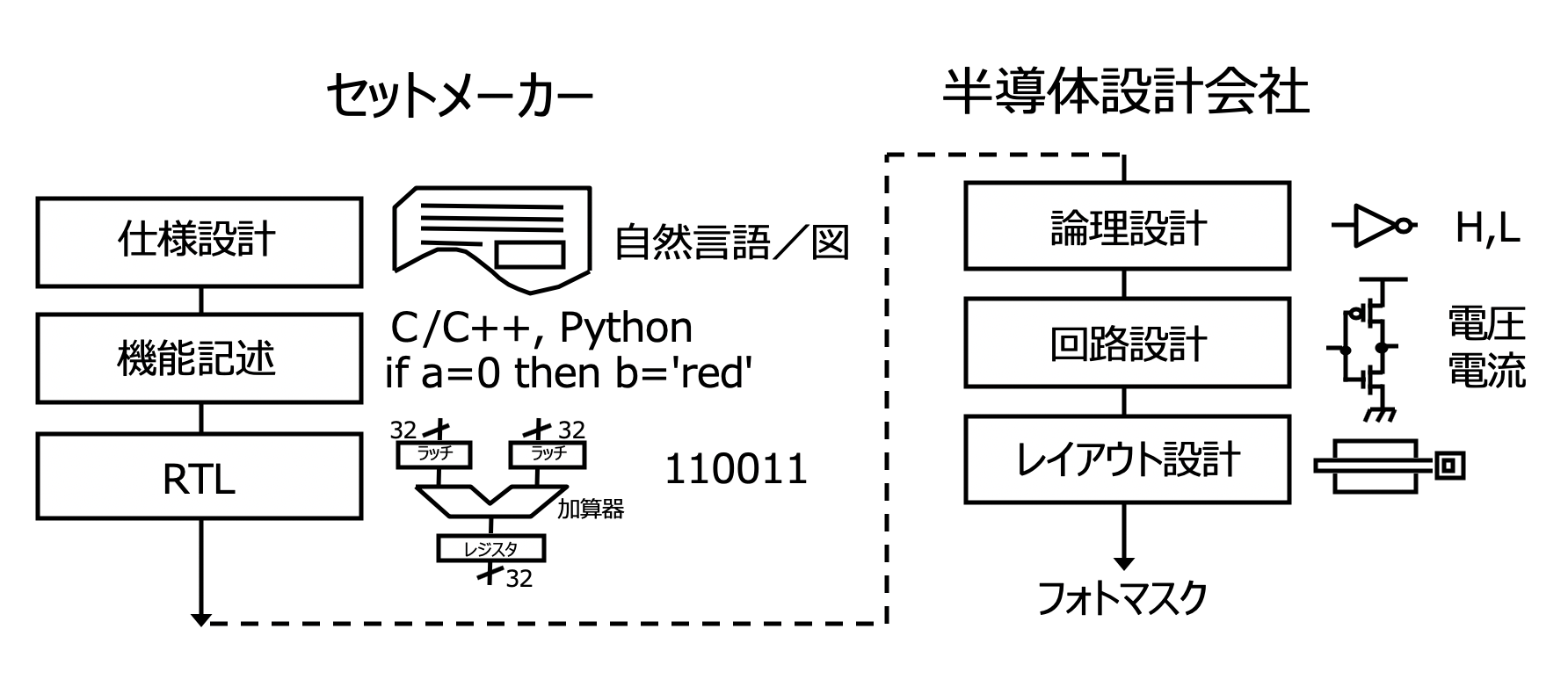

文章と図で著された仕様書をVerilogなどのハードウェア記述言語で書き、さらに処理手順をクロックサイクルごとに分解したRTL(レジスタ転送レベル)記述に書き下します。そして、論理設計、回路設計、レイアウト設計を経て、最終的にはフォトマスクの幾何学的模様を描きます。このようにチップの設計は、抽象度を順次下げていく変換作業です。

チップのユーザーであるセットメーカがRTLまでを設計し(フロント・エンド設計)、半導体設計会社が論理設計以下(バック・エンド設計)を行う分業体制ができています。

設計効率を上げるためにコンピュータを利用した自動設計が、情報量の格段に多い下流から順次導入されてきました。1970年代にマスク設計、1980年代にレイアウト設計、1990年代に論理設計が自動化されました。システム設計を自動化する高位合成も1990年頃から研究が始まり2010年頃から一部で実用が始まっています。

しかし、システム設計の効率を上げる一般的な方法は、RTLの再利用です。プロセッサコアやメモリコントローラのような汎用の機能は、設計資産(IP)として流通しています。また、専用回路のRTLもスクラッチから作るのではなく、過去に設計したRTLを再利用して組み上げます。

それでも最近の大規模なチップ、たとえばアップルのプロセッサA12には69億個のトランジスタが集積されていますが、こうしたチップの開発には数百人のエンジニアを配しても数年の歳月を要します。そして開発費は数100億円にも及びます。

集積度は指数関数的に増大しています。従来の開発方法はそろそろ限界です。

加えて、AIが登場しました。AIは日進月歩で進化しており、去年の技術は見劣りします。年単位の期間と数百億円の費用を要するチップ開発はリスクが高すぎます。

チップのアジャイル開発

私たちは、チップのユーザーが行うシステム設計・検証にもアジャイル開発の手法を適用できると考えています。

システムを小さな単位に分けてC/C++やPythonで記述した後に、高位合成ツールでRTLを自動生成しながら、ボトムアップにシステムを組み上げるのです。

ソフトウェアを書くようにチップをアジャイル開発できるので、セットメーカの開発期間と費用を大幅に短縮でき、開発リスクを軽減できます。

高位合成ツールは、回路性能とレイアウト面積を変えたさまざまなRTLを一瞬に生成できます。これを用いて性能と面積のトレードオフを探索しながら最適なRTLを設計し、次にFPGAに実装したりあるいはASIC用のシミュレータでテストしながら、短期間で機能のリリースを繰り返すことができます。

従来の手法では、設計者が仕様を深く理解した上でブロック図を描き、各ブロックの性能や信号接続の混雑度などを綿密に計算してから設計に着手していました。しかし設計の初期段階で性能や面積を見積もることは難しく、勘と経験に頼ることになります。そしてなにより、システムが複雑になると人手に負えなくなります。

アジャイルな開発手法では、小さな単位に分けた機能ブロックをコンピュータが自動設計と検証を繰り返しながらリリースしていきます。

リリースされた機能ブロックをボトムアップに組み上げていくのもコンピュータで自動化できます。高位合成を用いれば、各機能ブロックに分散して制御機構を持たせることができるので、機能ブロックを接続して全体の制御を組み上げることができるからです。

つまり、ソフトウェアの並列分散プログラムのように、機能ブロックを組み上げて大規模なチップを作ることができます。

C/C++やPythonで記述すると、RTL記述に比べて行数を1/100に短縮できます。したがって設計者が検討やシミュレーションをするのに要する労力や時間を桁違いに短縮できます。

高位記述では回路構造をパラメータで表現できるので、より幅広い実装ができると共に、実装範囲、つまり機能、性能、インターフェースプロトコルの設定幅を予め把握できます。

加えて、設計記述と双対する検証モデルを一緒に用意しておけば、変更範囲の確認が容易になるだけでなく、設計と同時に検証環境を効率的に組み上げることができます。つまり、設計と検証の両輪に跨ったアジャイル開発ができます。

この手法では、専用の制御回路で機能ブロックを接続するので、エネルギー効率を高くできます。IPをCPUバスに接続してCPUが中央制御する従来の方法では、5G(通信)やH.265(動画圧縮)やWPA2 (暗号)のような複雑な処理に対して高い性能を引き出すことができません。

また、従来手法では別のプロジェクトでも再利用するつもりでRTLを設計するので、必用以上に高性能な回路を設計しがちですが、高位合成を用いるとプロジェクト毎に最適な性能と面積の回路をその都度自動生成できます。

Divide and Conquer

U.C. BerkeleyのCADの授業で最初に学んだのはDivide and Conquerでした。複雑な問題でも、同様の小さな問題に分割しそれぞれを解決した上で組み合わせれば、解決策を導けるという考え方です。コンピュータアルゴリズムの多くがこの思想で設計されています。

問題の分割、解法、結果の組合せは、再帰的手法で行います。その結果、計算時間が飛躍的に短縮されます。

たとえば、並び替えのアルゴリズムの計算オーダーを比べると、バブルソートがO(n2)であるのに対して、Divide and Conquerを用いたクイックソートはO(nlog2n)に計算時間を短縮できます。nが1,000のとき1,000,000が9,966になるのですから1/100に短縮できます。検索でも、リニアサーチのO(n)からバイナリーサーチのO(log2n)に時間短縮できます。

AI時代に求められるのは素早い試行錯誤です。大量のデータをAIで分析してモデルを見つけ、そのモデルを素早く実装してさらにデータを集めて分析し、改善を繰り返す。こうした試行錯誤を手際よく行うことが肝要です。

アジャイルと大規模設計、この背反する制約下でAI時代に合ったチップ開発法を創出しなければなりません。

アジャイル開発においてもデータ収集においても中国から学ぶところが多くなりました。そう言えば、中国からの留学生がよく私に「先生、念入りに準備しすぎよ」と言っていたのを思い出します。