同期と非同期

チップのリズム

2020.06.10

チップの同期設計

半世紀前、クロックを用いて回路のタイミングを揃える同期設計と、そうしない非同期設計の是非が議論されていました。

カリフォルニア工科大学では次のような実験が行われました。一般の学生にはチップを同期設計する課題を与え、成績優秀者には同じチップを非同期で設計するように指示したのです。その結果、同期設計の方は多くのチップが正しく動作しましたが、非同期設計の方は正しく動作しませんでした。非同期設計で何が起きたのでしょうか?

論理回路には、入力が決まると出力が一意に決まる組合せ論理回路と、入力が同じでも状態によって出力が変わる順序論理回路があります。計算はいつも答えが同じなので組合せ論理回路を使いますが、制御は状態によって動作を変える必要があるので順序論理回路を用います。

状態は遷移します。たとえば2ビットで表現される状態{S1, S2}が{0,1}の状態から{1,0}の状態に遷移する際に、意図しない{0,0}や{1,1}の状態を一瞬経由します。なぜならS1とS2は違う回路の出力だから、あるいは全く同じ回路の出力だとしても回路の素子には製造ばらつきがあるので、両者のタイミングを揃えることは困難だからです。

この一瞬のためらい(ダイナミックハザード)は、計算では最終的に正しい答えを導くので問題になりませんが、制御では誤動作の原因になります。ためらった瞬間にデータが到着すると制御を誤るからです。

そこで、ちょうど交通信号機が青になると一斉にクルマが発進するように、早く到着したデータも遅く到着したデータも一旦待たせて、クロックが変化した瞬間にデータを一斉に出力すれば、クロックの周期(サイクル)毎にタイミングを揃えることができます。

データは2つのインバータで輪を作れば保持できます。たとえば1つ目のインバータにLが入力するとその出力はHになり、2つ目のインバータでHがLになって、1つ目のインバータの入力にLを戻すからです。

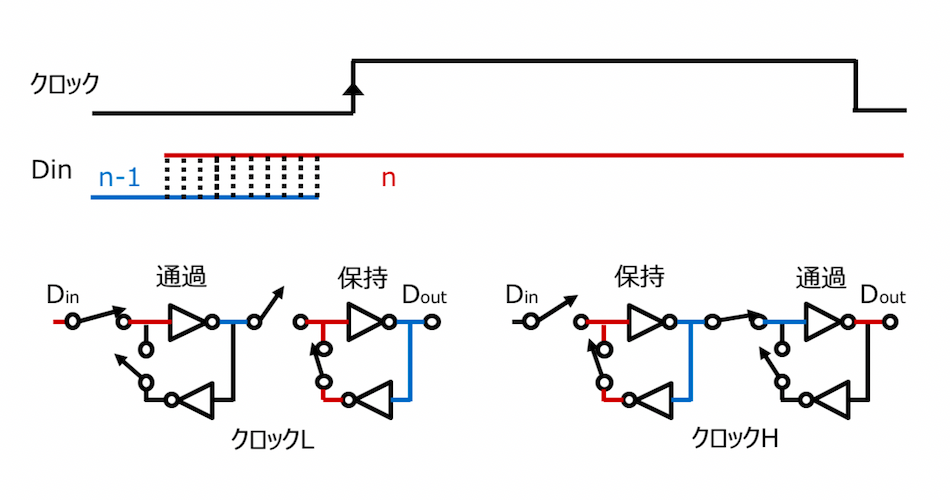

クロックで開閉するスイッチをこの輪に挟み、クロックがLのときは輪が閉じてデータを保持し、クロックがHのときは輪が開いてデータを通過させるようにします。この回路をラッチと言います。掛け金のようにデータをひっかけることができるからです。

ラッチを2つ繋げて前のラッチに逆相のクロックを与えた回路をフリップフロップと言います。クロックがLのときは、前段のラッチがデータを通過させ後段のラッチは以前のデータを保持していますが、クロックがHに変化すると、前段のラッチはその時点のデータを保持して後段のラッチがそのデータを通過させるので、この瞬間にデータが一斉にフリップフロップから出力されます。

ちなみに、クロックがHからLに変化するときは、前段のラッチが次のデータを通過させますが後段のラッチがそれよりも一瞬早く現在のデータを保持しますから、フリップフロップの出力には現在のデータが保持されたままで、次のデータは待たされます。

フリップフロップを使うとクロックのサイクル毎にタイミングを検証できるので検証コストを低く抑えることができます。一般のチップはフリップフロップを採用しています。

一方、ラッチを用いるとクロックがHの間はデータが通過できるので、どこかのサイクルで遅れが生じても後で挽回できます。しかしタイミング検証は、過去のサイクルまで遡って調べ上げる必要があるため、検証コストが高くなります。プロセッサはラッチを採用しています。

非同期設計の再考

チップの性能を高めるためには、精緻なタイミング設計が必要です。論理回路の信号伝搬遅延が素子の製造ばらつきや電源電圧および温度の変動から受ける影響と、クロックを生成したときのゆらぎ(ジッタ―)や分配したときの時差(スキュー)を計算して、目標とする製造歩留まりに必要なタイミング余裕を設計で保証します。

この設計余裕は、デバイスの微細化と電源電圧の低下に伴い増大します。そして、クロックが高速になるほど、Timing closureと呼ばれるタイミング設計のコストも増大します。

同期設計では、一番遅い回路(クリティカルパス)がクロックの周期を決めるので、それ以外の大半の回路は性能に影響しません。一方で、クロックの分配やフリップフロップだけで、電力の1/4から1/2を消費します。

このような同期設計のコストや無駄が顕著になる中、クロック周波数が1GHzを超えた頃から非同期設計を見直す研究が始まりました。Ivan Sutherlandが“Computers without Clocks - Asynchronous chips improve computer performance by letting each circuit run as fast as it can” という論文を発表したのが2002年です。Sun MicrosystemsのUltraSPARC IIIiの一部に非同期回路が使われました。

Sutherlandは、コンピュータグラフィックスの父と呼ばれる天才です。彼はチップの設計にも精通しています。1999年に論理回路の遅延モデルLogical Effortを提唱しました。優れたモデルなので、私はこれを授業で教えています。

彼は、電界結合を用いたチップ間接続も2003年に論文発表しています。私たちが磁界結合を用いたチップ間接続の研究を始めた頃でした。2007年に私がUC. BerkeleyのMacKay Professorになったとき、教員会議で彼と同席できたことは光栄でした。

閑話休題、非同期回路は二線式論理を用いて、2つの出力が等しい間は計算中であり、出力の一方が変化したときに計算完了の信号と計算結果を次の回路に伝えます。

当然、非同期設計は同期回路よりも多くのトランジスタと配線を使いますが、同期設計の無駄に比べれば得になるときが来るかも知れません。

私はそれが7nm世代だろうと考えていました。しかし、トランジスタのゲート支配力を高めたFinFETの性能が予想以上に良く、7nmでは非同期設計の逆転は確認できませんでした。トランジスタの構造改革は今後も続きそうなので、非同期設計が使われる機会はしばらく先になるかも知れません。

ただし、AIで注目されている神経回路網などの布線論理による並列データ処理は、非同期設計に向いています。(そう言えば、私たちは一瞬どころか何度もためらい、そして誤った判断もしています。)

自然界のリズム

1665年のある日、Christiaan Huygens(光の波動説に基づく「ホイヘンスの原理」の発見者)は部屋の壁に並べて掛けてある二つの時計の振り子が同期していることに偶然気付きました。一方の振り子が右に振れるとき他方は必ず左に振れます。わざとタイミングを乱しても、しばらくすると必ず同期します。

ところが、二つの時計を離れた壁に掛けると、同期は起こりません。Huygensは、二つの時計の間にごく弱い相互作用が働いていることが原因ではないかと推察しました。

この世にはリズムがあふれています。そしてリズムとリズムが出会うと、互いに同期します。

たとえば、つり橋を歩くと人々の歩調が思わず重なって橋が大きく揺れます。ロンドンのテムズ川に架かるミレニアム・ブリッジが2000年に大揺れしました。流行や渋滞も同期現象に根差しています。

昆虫や細胞にも同期は起こります。東南アジアでは、無数のホタルがマングローブの森に集まって一斉に明滅します。

哺乳類では、脳の視床下部にある視交叉上核で2万個程の時計細胞が協調して体内時計を作り、睡眠周期などのリズムを生み出しています。心臓では、1万個程のペースメーカー細胞がたゆまず同期発火して、生涯に30億回の心拍をしっかりと刻んでいます。

心を持たない無生物も同期します。超電導状態では、無数の電子が歩調を合わせて進み電気抵抗がほぼゼロになります。レーザが強力な光の束になるのも、無数の原子が位相と振動数のそろった光子を放出するからです。

一方、夜空の月にウサギがいつでも見えるのは、月の自転と公転が同期して常に地球に同じ側を向けているからです。また、太陽系内の惑星の重力が同期して一致することで、小惑星帯から地球目掛けて隕石群が吐き出されることがあり、その結果、恐竜は絶滅しました。

同期現象は、人間が作り出したネットワークや仮想空間にも存在します。高圧送電線網に接続された発電機は、おのずと同期します。回転速度の高い発電機から低い方へエネルギーが流れて速度の調整が行われるからです。その結果、異常が連鎖して事故に繋がります。また、インターネットでもルータがホタルのように同期してトラフィックが急激に変動する現象が以前は見られました。

同期を制御しようという最初の工学的な試みは、1978年にRobert Adlerが著した発振回路の周波数引き込み現象に関する解析です。

三つ以上の回路の結合同期を最初に試みたのは、おそらく私たちの研究グループです。2006年に、一つのチップに集積された四つの発振器の出力を伝送線路で結び、結合同期させることに成功しました。次に2010年に、四つのチップを積層し、チップ間を磁界結合した状態で集団同期現象を発見し、これを利用して各チップにクロックを正確に分配する技術を開発しました。

こうした集団同期現象は、非線形科学によって解明されつつあります。